fram till denna punkt, vår analys av transistor logiska kretsar har begränsats till TTL design paradigm, varigenom bipolära transistorer används, och den allmänna strategin för flytande ingångar som motsvarar ”hög” (ansluten till VCC) ingångar—och motsvarande, ersättningen för ”open-collector” utgångssteg—bibehålls. Detta är dock inte det enda sättet vi kan bygga logiska grindar.,

fälteffekttransistorer

fälteffekttransistorer, särskilt den isolerade grindvarianten, får användas vid utformningen av grindkretsar. Att vara spänningsstyrda snarare än strömstyrda enheter tenderar IGFETs att tillåta mycket enkla kretsdesigner. Ta till exempel följande inverterkrets byggd med P-och N-kanals IGFETs:

Lägg märke till ”vdd” – etiketten på den positiva strömförsörjningsterminalen., Denna etikett följer samma konvention som ” Vcc ” i TTL-kretsar: den står för den konstanta spänningen som appliceras på avloppet av en fälteffektstransistor, med hänvisning till marken.

fälteffekttransistorer i grindkretsar

låg ingång

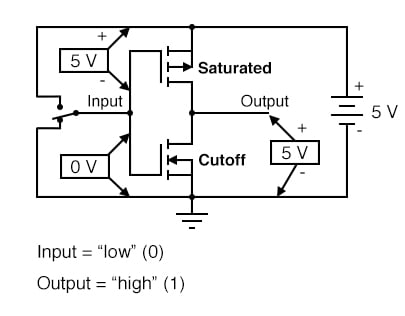

låt oss ansluta denna grindkrets till en strömkälla och ingångsomkopplare och undersöka dess funktion. Observera att dessa igfet transistorer är E-typ (Enhancement-mode), och så är normalt-off enheter.

det tar en applicerad spänning mellan grind och avlopp (faktiskt mellan grind och substrat) av rätt polaritet för att bias dem på.,

den övre transistorn är en P-kanal IGFET. När kanalen (substratet) görs mer positiv än porten (gate negativ i förhållande till substratet), kanalen förbättras och strömmen är tillåten mellan källa och avlopp.

så, i ovanstående illustration, är den övre transistorn påslagen. Den nedre transistorn, som har nollspänning mellan grind och substrat (källa), är i sitt normala läge: av.,

sålunda är verkan av dessa två transistorer sådana att grindkretsens utgångsplint har en fast anslutning till Vdd och en mycket hög motståndsanslutning till jord. Detta gör utgången ” hög ”(1) för” låg ” (0) tillstånd av ingången.,

hög ingång

därefter flyttar vi ingångsomkopplaren till sin andra position och ser vad som händer:

nu är den nedre transistorn (n-kanalen) mättad eftersom den har tillräcklig spänning av den korrekta polariteten applicerad mellan grind och substrat (kanal) för att slå på den (positiv på grinden, negativ på kanalen). Den övre transistorn, som har nollspänning applicerad mellan porten och substratet, är i sitt normala läge: av.

således är utgången för denna grindkrets nu ”låg” (0)., Uppenbarligen uppvisar denna krets beteendet hos en inverter, eller inte Grind.

komplementära Metalloxidhalvledare (CMOS)

användning av fälteffektstransistorer istället för bipolära transistorer har i hög grad förenklat utformningen av inverterporten. Observera att utgången från denna port aldrig flyter som är fallet med den enklaste TTL-kretsen: den har en naturlig ”totem-pole” – konfiguration, som kan både sourcing och sjunkande Lastström.

nyckeln till denna gate krets eleganta design är den kompletterande användningen av både P – och N-kanal IGFETs., Eftersom IGFETs är mer allmänt kända som MOSFETs (metalloxid-Semiconductor Field Effect Transistor), och denna krets använder både p-och N – kanal transistorer tillsammans, den allmänna klassificeringen ges till gate kretsar som denna är CMOS: kompletterande metalloxid halvledare.

CMOS Gates: utmaningar och lösningar

CMOS-kretsar plågas inte av de inneboende nonlineariteterna hos fälteffektstransistorer, eftersom deras transistorer som digitala kretsar alltid arbetar i antingen de mättade eller avstängningslägena och aldrig i det aktiva läget., Deras ingångar är emellertid känsliga för höga spänningar som genereras av elektrostatiska (statisk elektricitet) källor, och kan även aktiveras i ”hög” (1) eller ”låg” (0) tillstånd av falska spänningskällor om de lämnas flytande.

av denna anledning är det olämpligt att tillåta en CMOS logic gate-ingång att flyta under några omständigheter. Observera att detta skiljer sig mycket från beteendet hos en TTL-Grind där en flytande ingång säkert tolkades som en” hög ” (1) logiknivå.,

CMOS problem med flytande ingångar

detta kan orsaka ett problem om ingången till en CMOS logic gate drivs av en enda kast switch, där ett tillstånd har ingången stabilt ansluten till antingen Vdd eller marken och det andra tillståndet har ingången flytande (inte ansluten till något):

det här problemet uppstår också om en CMOS gate-ingång drivs av en öppen samlare TTL Gate., Eftersom en sådan TTL-grinds utgång flyter när den går ”hög” (1), kommer CMOS-porten att lämnas i ett osäkert tillstånd:

lösning på flytande ingångar

Pullup motstånd

lyckligtvis finns det en enkel lösning på detta dilemma, en som används ofta i CMOS logiska kretsar., När en enda kastbrytare (eller någon annan typ av gateutgång som inte kan både sourcing och sjunkström) används för att driva en CMOS-ingång, kan ett motstånd som är anslutet till antingen Vdd eller jord användas för att ge en stabil logiknivå för det tillstånd där drivanordningens utgång är flytande.

detta motstånd värde är inte kritiskt: 10 kΩ är vanligtvis tillräckligt., När det används för att tillhandahålla en ”hög” (1) logisk nivå i händelse av en flytande signalkälla, är detta motstånd känt som ett pullupmotstånd:

Pulldown motstånd

När ett sådant motstånd används för att ge en ”låg” (0) logisk nivå i händelse av en flytande signalkälla, är det känt som ett pulldown motstånd., Återigen är värdet för ett pulldown-motstånd inte kritiskt:

eftersom Open-collector TTL-utgångar alltid sjunker, aldrig källa, ström, pullup-motstånd är nödvändiga när de interagerar med en sådan utgång till en CMOS-grindingång:

flera Pullup-och Pulldown-motstånd

även om CMOS-grindarna som användes i de föregående exemplen var alla växelriktare (single-input), gäller samma princip för pullup och pulldown motstånd för flera ingångs CMOS-grindar., Naturligtvis krävs ett separat pullup-eller pulldown-motstånd för varje gate-ingång:

detta leder oss till nästa fråga: hur utformar vi flera CMOS-portar som och, NAND, eller och NOR? Inte överraskande avslöjar svaret på denna fråga en enkelhet av design som liknar CMOS-omriktaren över dess TTL-ekvivalent.,

CMOS NAND Gates

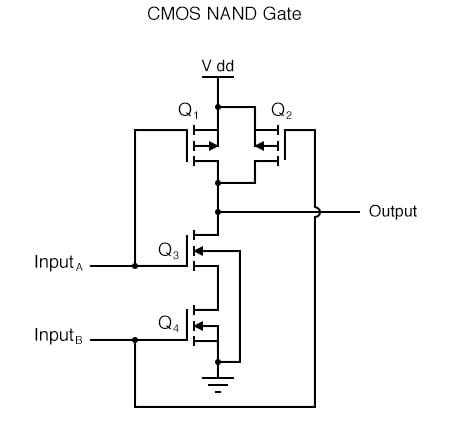

här är till exempel schematiskt diagram för en CMOS NAND gate:

Lägg märke till hur transistorer Q1 och Q3 liknar det seriekopplade komplementära paret från inverterkretsen. Båda styrs av samma ingångssignal (ingång A), den övre transistorn stängs av och den nedre transistorn slås på när ingången är ”hög” (1) och vice versa.,

lägg också märke till hur transistorer Q2 och Q4 styrs på samma sätt av samma ingångssignal (ingång B), och hur de också kommer att uppvisa samma on/off-beteende för samma ingångslogiknivåer. De övre transistorerna i båda paren (Q1 och Q2) har sina käll-och dräneringsterminaler parallellt, medan de nedre transistorerna (Q3 och Q4) är seriekopplade.

vad detta innebär är att utgången kommer att gå ” hög ”(1) om antingen topp transistor mättar, och kommer att gå” låg ” (0) endast om båda lägre transistorer mätta.,

CMOS-Kretsbeteenden för alla logiska ingångar

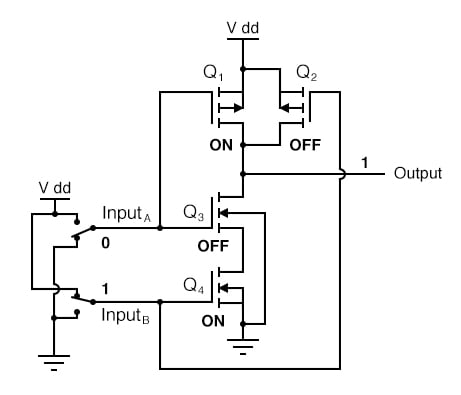

följande sekvens av illustrationer visar beteendet hos denna NAND-port för alla fyra möjligheter till ingångslogiknivåer (00, 01, 10 och 11):

CMOS och Gate

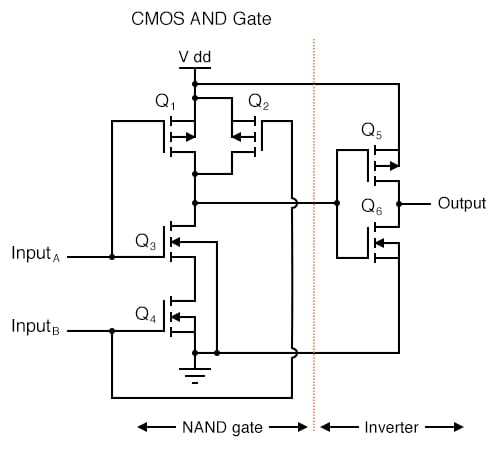

som med TTL NAND Gate kan CMOS NAND Gate-kretsen användas som utgångspunkt för skapandet av An och gate., Allt som behöver läggas till är ett annat steg av transistorer för att invertera utgångssignalen:

CMOS eller Gates

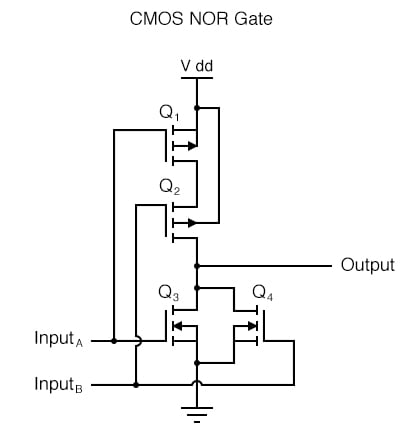

en CMOS eller gate-krets använder fyra MOSFET precis som NAND-porten, förutom att dess transistorer är annorlunda ordnade., I stället för två parallella sourcing (övre) transistorer anslutna till Vdd och två seriekopplade sjunkande (nedre) transistorer anslutna till marken, NOR gate använder två seriekopplade sourcing transistorer och två parallellkopplade sjunkande transistorer så här:

som med NAND gate, transistorer Q1 och Q3 fungerar som ett komplementärt par, liksom transistorer Q2 och Q4. Varje par styrs av en enda ingångssignal., Om antingen ingång A eller ingång B är ”hög” (1), kommer minst en av de nedre transistorer (Q3 eller Q4) vara mättad, vilket gör utgången ”låg” (0).

endast om båda ingångarna är ” låga ”(0) kommer båda nedre transistorer att vara i avstängningsläge och båda övre transistorer att mättas, de villkor som är nödvändiga för att utmatningen ska gå” höga ” (1). Detta beteende definierar naturligtvis den nor logiska funktionen.

CMOS eller Gates

OR-funktionen kan byggas upp från basic NOR gate med tillägg av ett invertersteg på utgången:

TTL vs., CMOS: fördelar och nackdelar

eftersom det verkar som om någon port som är möjlig att konstruera med TTL-teknik kan dupliceras i CMOS, varför samexisterar dessa två ”familjer” av logisk design fortfarande? Svaret är att både TTL och CMOS har sina egna unika fördelar.

först och främst på listan över jämförelser mellan TTL och CMOS är frågan om strömförbrukning. I detta mått av prestanda är CMOS den obestridda segraren., Eftersom de kompletterande p-och N-kanals MOSFET-paren av en CMOS-grindkrets (helst) aldrig leder samtidigt, finns det liten eller ingen ström som dras av kretsen från vdd-strömförsörjningen förutom vilken ström som är nödvändig för att källa ström till en belastning. TTL, å andra sidan, kan inte fungera utan någon ström som dras hela tiden, på grund av förspänningskraven för de bipolära transistorer från vilka den är gjord.

det finns dock en varning till denna fördel., Medan strömförlusten hos en TTL-Grind förblir ganska konstant oberoende av dess driftstillstånd(er), släpper en CMOS-Grind mer ström när frekvensen av dess ingångssignal(er) stiger. Om en CMOS-Grind drivs i ett statiskt (oföränderligt) tillstånd, släpper det nollkraft (helst).

CMOS-portkretsar drar emellertid övergående ström under varje utgångstillståndsomkopplare från ”låg” till ”hög” och vice versa. Så, ju oftare en CMOS gate växlar lägen, desto oftare kommer det att dra ström från vdd-tillförseln, därmed större effektförlust vid större frekvenser.,

fördelar med CMOS

en CMOS gate drar också mycket mindre ström från en driving gate utgång än en TTL gate eftersom MOSFETs är spänningsstyrda, inte strömstyrda, enheter. Detta innebär att en grind kan driva många fler CMOS-ingångar än TTL-ingångar. Måttet på hur många Grind ingångar en enda Grind utgång kan köra kallas fanout.

en annan fördel som CMOS gate designs njuta av över TTL är ett mycket bredare tillåtet utbud av nätspänningar. Medan TTL gates är begränsade till strömförsörjning (Vcc) spänningar mellan 4.75 och 5.,25 volt, CMOS grindar är vanligtvis kunna arbeta på någon spänning mellan 3 och 15 volt!

orsaken till denna skillnad i strömförsörjningsspänningar är de respektive förspänningskraven för MOSFET kontra bipolära korstransistorer. MOSFETs styrs uteslutande av grindspänning (med avseende på substrat), medan BJTs är strömstyrda enheter.

TTL gate circuit resistances beräknas exakt för korrekta biasströmmar förutsatt en 5 volt reglerad strömförsörjning., Eventuella signifikanta variationer i den nätspänningen kommer att leda till att transistorns biasströmmar är felaktiga, vilket sedan resulterar i opålitlig (oförutsägbar) Drift.

den enda effekten som variationer i nätspänningen har på en CMOS-Port är spänningsdefinitionen för ett ”högt” (1) tillstånd. För en CMOS-grind med 15 volt nätspänning (Vdd) måste en insignal vara nära 15 volt för att betraktas som ”hög” (1). Spänningsgränsen för en” låg ” (0) signal förblir densamma: nära 0 volt.,

nackdelar med CMOS

en bestämd nackdel med CMOS är långsam hastighet, jämfört med TTL. Ingångskapaciteten hos en CMOS-grind är mycket, mycket större än för en jämförbar TTL-Grind—på grund av användningen av MOSFETs snarare än BJTs-och så kommer en CMOS-Grind att vara långsammare för att svara på en signalövergång (låg till hög eller vice versa) än en TTL-Grind, alla andra faktorer är lika.,

RC – tidskonstanten som bildas av kretsmotstånd och grindens ingångskapacitans tenderar att hindra den snabba uppgången-och falltiden för en digital logiknivå och därigenom försämra högfrekvent prestanda.

strategier för att bekämpa nackdelarna

en strategi för att minimera denna inneboende nackdel med CMOS gate-kretsar är att ”buffra” utsignalen med ytterligare transistorsteg, för att öka enhetens totala spänningsförstärkning., Detta ger en snabbare övergångsspänning (hög till låg eller låg till hög) för en ingångsspänning som långsamt förändras från ett logiskt tillstånd till ett annat.

Tänk på detta Exempel, av en ”obuffrad” eller grind mot en ”buffrad” eller B-serie, eller gate:

i huvudsak lägger designförbättringen i b-serien till två växelriktare till utgången av en enkel eller krets., Detta tjänar inget syfte när det gäller digital logik, eftersom två cascaded inverters helt enkelt avbryter:

men att lägga till dessa invertersteg i kretsen tjänar till att öka den totala spänningsförstärkningen, vilket gör utgången mer känslig för förändringar i ingångstillstånd, som arbetar för att övervinna den inneboende långsamhet som orsakas av CMOS-ingångskapacitansen.

recension:

- CMOS logiska grindar är gjorda av IGFET (MOSFET) transistorer snarare än bipolära korstransistorer.

- CMOS gate-ingångar är känsliga för statisk elektricitet., De kan skadas av höga spänningar, och de kan anta någon logisk nivå om de lämnas flytande.

- Pullup och pulldown motstånd används för att förhindra en CMOS gate ingång från flytande om drivs av en signalkälla som endast kan sourcing eller sjunkande ström.

- CMOS-grindar släpper ut mycket mindre ström än motsvarande TTL-grindar, men deras effektförlust ökar med signalfrekvens, medan effektförlusten hos en TTL-grind är ungefär konstant över ett brett spektrum av driftsförhållanden.,

- CMOS gate-ingångar drar mycket mindre ström än TTL-ingångar, eftersom MOSFETs är spänningsstyrda, inte strömstyrda, enheter.

- CMOS gates kan arbeta på ett mycket bredare utbud av nätspänningar än TTL: typiskt 3 till 15 volt mot 4,75 till 5,25 volt för TTL.

- CMOS-grindar tenderar att ha en mycket lägre maximal arbetsfrekvens än TTL-grindar på grund av ingångskapacitanser som orsakas av MOSFET-grindarna.

- b-serien CMOS gates har ”buffrade” utgångar för att öka spänningsförstärkningen från ingång till utgång, vilket resulterar i snabbare utgångssvar på ingångssignalförändringar., Detta bidrar till att övervinna den inneboende långsamhet av CMOS grindar på grund av MOSFET ingångskapacitans och RC tidskonstant därigenom skapas.