Opp til dette punktet, vår analyse av transistor logikk-kretser har vært begrenset til TTL design paradigme, der bipolare transistorer er brukt, og den generelle strategi av flytende innganger være ekvivalent til «høy» (koblet til Vcc) – innganger—og tilsvarende godtgjørelse av «open collector» output stadier—er opprettholdt. Men, dette er ikke den eneste måten vi kan bygge logiske porter.,

Felt-Effekt Transistorer

Felt-effekt transistorer, spesielt isolert-gate utvalg, kan bli brukt i utforming av gate-kretser. Blir spenning-kontrollerte snarere enn nåværende-kontrollerte enheter, IGFETs har en tendens til å tillate veldig enkel krets design. Ta for eksempel følgende inverter kretsen bygget ved hjelp av P – og N-kanal IGFETs:

Merke til «Vdd» etiketten på den positive strømforsyning terminal., Denne etiketten følger samme konvensjon som «Vcc» i TTL-kretser: det står for konstant spenning tilføres avløpet fra et felt-effekt transistor, i referanse til bakken.

felteffekttransistorer i Gate Kretser

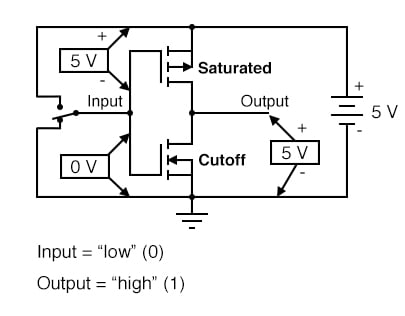

Lav Inngang

La oss koble til med denne gate krets til en strømkilde og inngangsvelger, og undersøke dets drift. Vær oppmerksom på at disse IGFET transistorer er E-type (Ekstrautstyr-modus), og så er vanligvis off-enheter.

Det tar en anvendt spenning mellom gate og drain (faktisk, mellom gate og substrat) for riktig polaritet for å påvirke dem på.,

Den øvre transistor er en P-kanal IGFET. Når kanalen (substrat) er gjort mer positive enn de gate (gate negative i forhold til underlaget), kanalen er forbedret og oppdatert er tillatt mellom source og drain.

Så, i illustrasjonen over toppen transistor er slått på. Den lavere transistor, etter å ha null spenning mellom gate og substrat (kilde), er i normal-modus: av.,

Dermed virkningen av disse to transistorer er slik at det utgang til gate kretsen har en solid tilkobling til Vdd og en svært høy motstand tilkobling til jord. Dette gjør output «høy» (1) til «lav» (0) tilstand av input.,

Høy Inngang

Neste, vil vi flytte inngang bytte til sin andre posisjon og se hva som skjer:

Nå lavere transistor (N-kanal) er mettet fordi det har tilstrekkelig spenning på riktig polaritet brukes mellom gate og substrat (kanal) for å slå det på (positivt på gate, negative på kanal). Øvre transistor, etter å ha null spenning brukt mellom gate og substrat, er i normal-modus: av.

Dermed resultatet av denne gate kretsen er nå «lav» (0)., Klart, dette krets utstillinger oppførselen til en inverter, eller IKKE-gate.

Complementary Metal Oxide Halvledere (CMOS -)

ved Hjelp av felt-effekt transistorer i stedet for bipolare transistorer i stor grad har forenklet design av omformeren gate. Vær oppmerksom på at resultatet av denne gate aldri flyter som er tilfelle med de enkleste TTL krets: det har en naturlig «totem poler» konfigurering, i stand til både å anskaffe og synker legg gjeldende.

– Tasten til denne porten krets ‘ elegante design er komplementære bruk av både P – og N-kanal IGFETs., Siden IGFETs er mer kjent som Mosfet (Metal-Oxide-Semiconductor Felt-Effekt Transistor), og denne kretsen bruker både P – og N-kanal transistorer sammen, generell klassifisering som er gitt til tor kretser som dette er CMOS: Complementary Metal Oxide Semiconductor.

CMOS Porter: Utfordringer og Løsninger

CMOS-kretser er ikke plaget av den iboende nonlinearities av felt-effekt transistorer, fordi som digitale kretser deres transistorer alltid bruke enten den mettede eller cutoff moduser og aldri i aktiv modus., Deres innganger er imidlertid følsom for høy spenning som genereres av elektrostatisk (statisk elektrisitet) – kilder, og kan også være aktivert i «høy» (1) eller «lav» (0) usa med falske spenning kilder hvis venstre flytende.

på grunn av dette, det er inadvisable å tillate en CMOS logikk gate inngang til å flyte under noen omstendigheter. Vær oppmerksom på at dette er svært forskjellig fra den oppførsel av en TTL gate hvor en flytende inngang var trygt tolkes som en «høy» (1) logikk nivå.,

CMOS Problemer med Flytende Innganger

Dette kan forårsake et problem hvis input til en CMOS logikk gate er drevet av en enkelt-kaste, slå, der en stat har inngang, solid koblet til enten Vdd eller bakken og den andre staten har inngang flytende (ikke koblet til noe som helst):

Også, dette problemet oppstår hvis en CMOS port inngang blir drevet av en åpen-kollektor TTL gate., Fordi en slik TTL gate produksjonen flyter når det går «høy» (1), CMOS port inngang vil være igjen i en usikker tilstand:

Løsning til Flytende Innganger

Pullup Motstander

Heldigvis, det er en enkel løsning på dette dilemmaet, som brukes ofte i CMOS logikk-kretser., Når et enkelt-kaste-bryteren (eller noen annen form for gate-utgang ute av stand til både å anskaffe og synker gjeldende) blir brukt til å drive en CMOS-inngang, en motstand som er koblet til enten Vdd eller jord kan benyttes til å gi en stabil logikk nivå for staten som kjører enheten utgang er flytende.

Denne motstanden er verdi er ikke kritisk: 10 kΩ er vanligvis tilstrekkelig., Når den brukes til å gi en «høy» (1) logikk nivå i tilfelle av en flytende signalkilde, denne motstanden er kjent som en pullup motstand:

Pulldown Motstander

Når en slik motstand er brukt for å gi en «lav» (0) logikk nivå i tilfelle av en flytende signalkilde, det er kjent som en pulldown motstand., Igjen, verdien for en pulldown motstanden er ikke kritisk:

Fordi open collector TTL utganger alltid vask, aldri kilde, strøm, pullup motstander er nødvendig når grensesnitt slik en utgang til en CMOS port inngang:

Flere Pullup og Pulldown Motstander

Selv om det CMOS porter som brukes i de foregående eksemplene var alle omformere (single-inngang), det samme prinsippet av pullup og pulldown motstander gjelder til flere-input CMOS porter., Selvsagt, en egen pullup eller pulldown motstanden vil være nødvendig for hver port inngang:

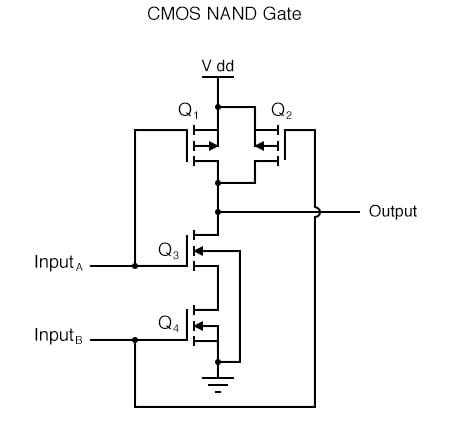

Dette bringer oss til det neste spørsmålet: hvordan kan vi designe multiple-input CMOS gates eksempel OG, NAND, ELLER, og HELLER? Ikke overraskende, er svaret(e) på dette spørsmålet, viser en enkelhet i design like mye at av CMOS inverter over sin TTL tilsvarende.,

CMOS NAND Portene

For eksempel, her er skjematisk diagram for en CMOS NAND gate:

Merke til hvordan transistorer Q1 og Q3 ligne serien-koblet komplementært par fra inverter krets. Begge er kontrollert av de samme inngangssignal (inngang A), øvre transistor å slå av og lavere transistor slå på når input er «høy» (1), og vice versa.,

legg også Merke til hvordan transistorer 2. Kvartal og 4. kvartal er på samme måte kontrolleres av samme inngangssignal (inngang B), og hvordan de vil også vise til de samme på/av-oppførsel for det samme inngang logikk nivåer. Øvre transistorer av begge parene (Q1 og Q2) har sin kilde og drain terminalene parallelt, mens den nedre transistorer (Q3 og Q4) er serien-koblet.

Hva dette betyr er at produksjonen vil gå «høy» (1) hvis en topp transistor mettet fett, og vil gå til «lav» (0) bare hvis både lavere transistorer mette.,

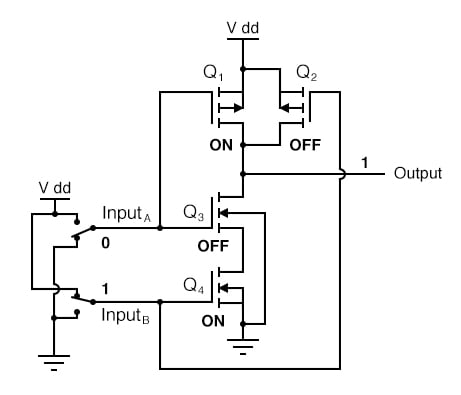

CMOS Krets Atferd for Alle Logiske Innganger

følgende sekvens av illustrasjonene viser den oppførsel av denne NAND porten for alle fire muligheter til innspill logikk nivåer (00, 01, 10 og 11):

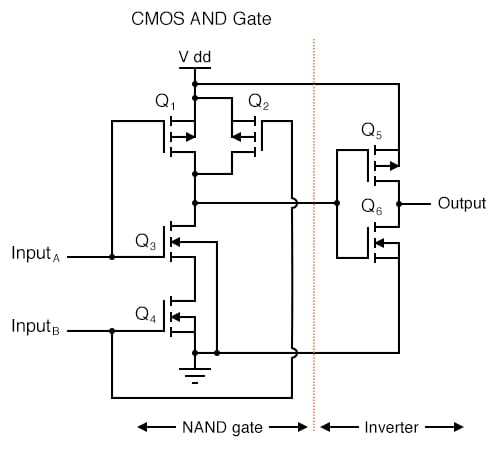

CMOS OG tor

Som med TTL NAND porten, CMOS NAND gate krets kan brukes som utgangspunkt for etablering av en OG gate., Alle som har behov for å bli lagt til, er et annet stadium av transistorer å snu utgangssignal:

CMOS ELLER Porter

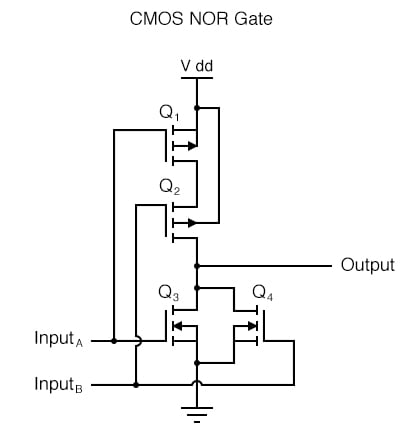

EN CMOS ELLER gate krets bruker fire Mosfet akkurat som NAND porten, bortsett fra at dets transistorer er ulikt organisert., I stedet for to parallell sourcing (øvre) transistorer som er koblet til Vdd og to serier som er koblet synker (lavere) transistorer som er koblet til jord, NOR porten bruker to serier som er koblet sourcing transistorer og to parallelle forbindelser synker transistorer som dette:

Som med NAND porten, transistorer Q1 og Q3 fungere som et komplementært par, som gjøre transistorer 2. Kvartal og 4. kvartal. Hvert par er kontrollert av en enkelt inngangssignal., Hvis en legger inn En eller inngang B er «høy» (1), minst ett av de lavere transistorer (Q3 eller Q4) vil bli mettet, og dermed gjør output «lav» (0).

Bare i tilfelle av begge inngangene er å være «lav» (0), vil både lavere transistorer være i cutoff-modus og både små transistorer være mettet, de nødvendige betingelsene for produksjon til å gå «høy» (1). Dette, selvfølgelig, definerer ELLER logikk funksjon.

CMOS ELLER Porter

ELLER funksjon kan være bygget opp fra grunnleggende HELLER gate med tillegg av en inverter scenen på output:

TTL vs., CMOS: Fordeler og Ulemper

Siden ser det ut til at noen gate mulig å lage ved hjelp av TTL-teknologi kan dupliseres i CMOS, hvorfor disse to «familier» av logikk design fortsatt eksistere? Svaret er at både TTL og CMOS har sine egne unike fordeler.

Først og fremst på listen av sammenligninger mellom TTL og CMOS-er spørsmålet om strømforbruk. I denne resultatmål, CMOS er uimotsagt victor., Fordi utfyllende P – og N-kanal MOSFET par av en CMOS port krets er (ideelt sett) aldri å gjennomføre på samme tid, det er lite eller ingen strøm tegnet av den krets fra Vdd strømforsyning bortsett fra det nåværende er nødvendig for å skaffe strøm til en belastning. TTL, på den annen side, kan ikke fungere uten noen strømtrekket til alle tider, på grunn av den vekting som trengs av bipolare transistorer som det er gjort.

Det er en påminnelse til denne fordelen, skjønt., Mens energitap av en TTL gate er fortsatt ganske konstant uavhengig av sin tilstand(s), en CMOS port forsvinner mer makt som frekvensen av sin inngangssignal(s) stiger. Hvis en CMOS port er operert i en statisk (uendret) tilstand, det forsvinner null strøm (ideelt sett).

Imidlertid CMOS gate kretser trekke transient strøm under hver utgang staten bytte fra «lav» til «høy» og vice versa. Så, jo oftere en CMOS port brytere-modusene, er de oftere vil det trekke strøm fra Vdd tilførsel, derav større energitap ved høyere frekvenser.,

Fordeler av CMOS –

– >

EN CMOS port også trekker mye mindre strøm fra en kjøring gate utgang enn en TTL gate fordi Mosfet er spenning-kontrollert, ikke gjeldende-kontrollert, enheter. Dette betyr at en gate kan kjøre mange flere CMOS-innganger enn TTL-innganger. Viser hvor mange gate innganger én gate utgang kan drive kalles fanout.

en Annen fordel at CMOS gate design nyte over TTL er en mye bredere tillatte utvalg av strømforsyning spenning. Mens TTL gates er begrenset til strømforsyningen (Vcc) spenning mellom 4.75 og 5.,25 volt, CMOS porter er vanligvis i stand til å operere på en spenning mellom 3 og 15 volt!

grunnen til At bak denne forskjellen i strømforsyning spenning er de respektive bias krav MOSFET versus bipolar junction transistorer. Mosfet styres utelukkende av gate-spenningen (med hensyn til substrat), mens Diode er gjeldende-kontrollerte enheter.

TTL gate krets styrker er nettopp beregnet for riktig bias strøm forutsatt en 5 volt regulert strømforsyning., Noen betydelige variasjoner i nettspenningen vil resultere i transistor bias strømninger blir feil, som så resulterer i upålitelige (uforutsigbare) drift.

Den eneste effekten at variasjoner i nettspenningen har på en CMOS port ligger spenningen definisjon av en «høy» (1) tilstand. For en CMOS port opererer på 15 volt nettspenning (Vdd), et inngangssignal må være nær 15 volt for å bli betraktet som «høy» (1). Spenningen terskelen for en «lav» (0) signalet forblir den samme: i nærheten 0 volt.,

Ulemper av CMOS –

– >

En bestemt ulempen med CMOS er langsom hastighet, sammenlignet med TTL. Input capacitances av en CMOS port er mye, mye større enn for et tilsvarende TTL gate—på grunn av bruken av Mosfet snarere enn Diode—og så en CMOS-porten vil være tregere til å svare på et signal overgang (low og high-eller vice versa) enn en TTL gate, alle andre faktorer er like.,

RC tid konstant dannet av kretsen motstand og innspill kapasitans av porten, har en tendens til å hindre rask økning – og høst-ganger av en digital logikk nivå, og dermed forringelse av høy frekvens ytelse.

Strategier for å Bekjempe Ulemper

En strategi for å minimere denne iboende ulempen med CMOS gate kretsene er å «buffer» utgangssignalet med ekstra transistor stadier, for å øke den generelle spenning gevinst på enheten., Dette gir en raskere overgang utgangsspenning (høy til lav eller lav til høy) for en inngangsspenning sakte endring fra en logikk-stat til en annen.

se på dette eksempelet, av en «ubufret» ELLER gate versus en «bufret» eller B-serien, og HELLER gate:

I hovedsak, B-serien design ekstrautstyr legger til to invertere til produksjon av en enkel ELLER krets., Dette tjener ingen hensikt, så langt som digital logikk er opptatt av, siden to cascaded invertere bare avbryte:

Imidlertid å legge til disse inverter stadier til den kretsen som ikke tjener den hensikt å øke det totale spenning få, noe som gjør produksjonen mer følsomme for endringer i inngang staten, som arbeider for å overvinne den iboende treghet forårsaket av CMOS port inngang kapasitans.

ANMELDELSE:

- CMOS-logiske porter er laget av IGFET (MOSFET) transistorer snarere enn bipolar junction transistorer.

- CMOS gate innganger er følsomme for statisk elektrisitet., De kan bli skadet av høye spenninger, og de kan påta seg noe som helst logikk nivå hvis venstre flytende.

- Pullup og pulldown motstander er brukt for å forhindre en CMOS port inngang fra flytende hvis det blir drevet av en signalkilde i stand bare for å anskaffe eller synker gjeldende.

- CMOS porter spre langt mindre strøm enn tilsvarende TTL gates, men deres energitap øker med signal frekvens, mens energitap av en TTL gate er tilnærmet konstant over et bredt spekter av driftsforhold.,

- CMOS gate innganger trekke langt mindre strøm enn TTL-innganger, fordi Mosfet er spenning-kontrollert, ikke gjeldende-kontrollert, enheter.

- CMOS porter er i stand til å operere på et mye bredere spekter av strømforsyning spenning enn TTL: vanligvis 3 til 15 volt versus 4.75 til 5,25 volt for TTL.

- CMOS porter har en tendens til å ha en mye lavere maksimal frekvens enn TTL-portene på grunn av input capacitances forårsaket av MOSFET gates.

- B-serien CMOS porter har «bufret» utganger for å øke spenningen få fra inngang til utgang, noe som resulterer i raskere utgang respons på input signal endres., Dette bidrar til å overkomme den iboende treghet i CMOS porter på grunn av MOSFET-inngang kapasitans og RC tid konstant og dermed skapt.