indtil dette punkt, vores analyse af transistor logik kredsløb har været begrænset til TTL design paradigme, hvorved bipolar transistorer er brugt, og den generelle strategi for flydende indgange svarende til “høj” (forbundet til Vcc) indgange—og tilsvarende godtgørelse af “open-collector” output faser, er opretholdt. Dette er imidlertid ikke den eneste måde, vi kan opbygge logiske porte på.,

felt-effekt transistorer

felt-effekt transistorer, især isoleret-gate sort, kan anvendes i udformningen af gate kredsløb. At være spændingsstyrede snarere end strømstyrede enheder, har IGFET ‘ er en tendens til at tillade meget enkle kredsløbsdesign. Tag for eksempel følgende inverter kredsløb bygget ved hjælp af P – og N-kanal IGFETs:

Bemærk “Vdd” – mærke på den positive strømforsyning terminal., Denne etiket følger den samme konvention som “Vcc” i TTL-kredsløb: det står for den konstante spænding, der påføres drænet af en felteffekttransistor, med henvisning til jorden.

Field Effect Transistorer i Gate kredsløb

lav indgang

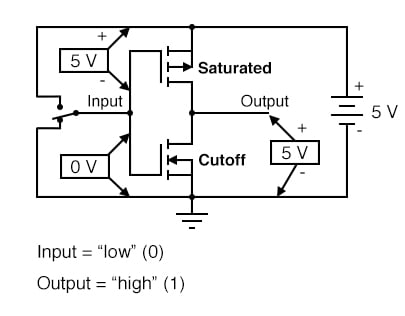

lad os forbinde dette gate kredsløb til en strømkilde og input s .itch, og undersøge dens funktion. Bemærk, at disse IGFET transistorer er E-type (Enhancement-mode), og så er normalt-off enheder.

det tager en påført spænding mellem gate og afløb (faktisk mellem gate og substrat) af den korrekte polaritet for at bias dem på.,

den øvre transistor er en P-kanal IGFET. Når kanalen (substrat) gøres mere positiv end porten (gate negativ i forhold til substratet), er kanalen forbedret og strøm er tilladt mellem kilde og afløb.

så i ovenstående illustration er den øverste transistor tændt. Den nedre transistor, der har nulspænding mellem Port og substrat (kilde), er i sin normale tilstand: slukket.,

virkningen af disse to transistorer er således sådan, at portkredsløbets udgangsterminal har en solid forbindelse til Vdd og en meget høj modstandsforbindelse til jorden. Dette gør udgangen ” høj “(1) for” lav ” (0) tilstand af input.,

High Input

Næste, vi vil flytte input skifte til den anden stilling og se hvad der sker:

Nu er den nederste transistor (N-kanal) er mættet, fordi det har tilstrækkelig spænding på den korrekte polaritet, der er anvendt mellem gate og substrat (kanal) for at tænde for den (positive på porten, negativ på den kanal). Den øvre transistor, der har nulspænding påført mellem sin port og substrat, er i sin normale tilstand: slukket.

således er udgangen af dette portkredsløb nu “lavt” (0)., Det er klart, at dette kredsløb udviser en inverters adfærd eller ikke Port.

komplementære metalo .idhalvledere (CMOS)

brug af felteffekttransistorer i stedet for bipolære transistorer har i høj grad forenklet designet af inverterporten. Bemærk, at udgangen af denne port aldrig flyder som det er tilfældet med det enkleste TTL-kredsløb: det har en naturlig “totem-pol” – konfiguration, der er i stand til både sourcing og synkende belastningsstrøm.nøglen til dette portkredsløbs elegante design er den komplementære brug af både P-og N-kanal IGFETs., Da IGFETs er mere almindeligt kendt som MOSFETs (Metal-Oxide-Semiconductor Field Effect Transistor), og dette kredsløb anvender både P – og N-kanal transistorer sammen, den generelle klassificering givet til gate kredsløb som dette er CMOS: Complementary Metal Oxide Semiconductor.

CMOS-Gates: Udfordringer og Løsninger

CMOS kredsløb, der ikke er plaget af den iboende nonlinearities af field-effekt transistorer, fordi som digitale kredsløb deres transistorer altid opererer i enten mættet eller cutoff tilstande og aldrig i aktiv tilstand., Deres indgange er imidlertid følsomme over for høje spændinger, der genereres af elektrostatiske (statiske elektricitet) kilder, og kan endda aktiveres i “høje” (1) eller “lave” (0) tilstande af falske spændingskilder, hvis de efterlades flydende.

af denne grund er det ikke tilrådeligt at tillade en CMOS logic gate-Indgang at flyde under alle omstændigheder. Bemærk, at dette er meget forskelligt fra opførelsen af en TTL-port, hvor en flydende indgang sikkert blev fortolket som et “højt” (1) logisk niveau.,

CMOS Problemer med Flydende Input

Dette kan være et problem, hvis input til en CMOS logik gate er drevet af en enkelt kaste skifte, hvor en medlemsstat har input solidt forbundet til enten Vdd eller jorden og den anden stat, der har input flydende (ikke forbundet til noget):

dette problem opstår, hvis en CMOS-gate input er drevet af en open-collector-TTL-porten., Fordi sådan en TTL-gate ‘ s output flyder, når det går “høj” (1), CMOS-gate input vil være tilbage i en usikker tilstand:

Løsning til Flydende Input

Pullup Modstande

Heldigvis er der en nem løsning på dette dilemma, som bruges hyppigt i CMOS logik kredsløb., Hver gang en enkeltkastkontakt (eller enhver anden form for portudgang, der ikke er i stand til både sourcing og synkende strøm) bruges til at drive en CMOS-indgang, kan en modstand, der er forbundet til enten Vdd eller jord, bruges til at tilvejebringe et stabilt logisk niveau for den tilstand, hvor køreenhedens output flyder.

denne modstands værdi er ikke kritisk: 10 K.er normalt tilstrækkelig., Når det bruges til at give en “høj” (1) logisk niveau i tilfælde af en flydende signal kilde, denne modstand er kendt som en pullup modstand:

Pulldown Modstande

Når en sådan modstand er brugt til at give en “lav” (0) logik plan i tilfælde af en flydende signal kilde, det er kendt som en pulldown modstand., Igen, værdien for en pulldown modstand er ikke kritisk:

Fordi open-collector-TTL output altid vasken, aldrig kilde, aktuelle, pullup modstande er nødvendige, når grænsefladerne sådan et output til en CMOS-gate input:

Flere Pullup og Pulldown Modstande

Selv om CMOS-porte, der anvendes i de foregående eksempler er alle invertere (single-input), det samme princip af pullup og pulldown modstande gælder for multiple-input CMOS-porte., Selvfølgelig, et separat pullup eller pulldown modstand vil være påkrævet for hver gate, input:

Dette bringer os til det næste spørgsmål: hvordan kan vi designe multiple-input CMOS-porte, såsom OG, NAND, ELLER, ELLER? Ikke overraskende afslører svaret / svarene på dette spørgsmål en enkelhed i design, der ligner CMOS-inverteren over dens ttl-ækvivalent.,

CMOS-NAND-Gates

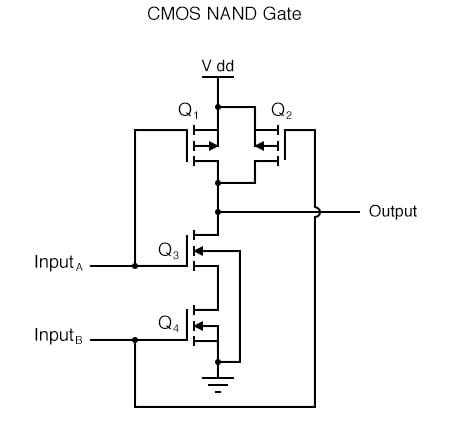

For eksempel, her er den skematiske diagram for en CMOS NAND-gate:

læg Mærke til, hvordan transistor Q1 og Q3 ligner serie-forbundet komplementære par fra inverter kredsløb. Begge styres af det samme indgangssignal (input a), den øvre transistor slukker og den nedre transistor tænder, når indgangen er “høj” (1) og omvendt.,

Bemærk også, hvordan transistorer22 og44 styres på samme måde af det samme indgangssignal (input B), og hvordan de også vil udvise den samme on / off-opførsel for de samme input-logikniveauer. De øverste transistorer i begge par (11 og22) har deres kilde-og drænterminaler parallelt, mens de nedre transistorer (33 og44) er serieforbundne.

hvad dette betyder er, at output vil gå “Høj” (1) hvis enten top transistor mætter, og vil gå “lav” (0) kun hvis begge lavere transistorer mætter.,

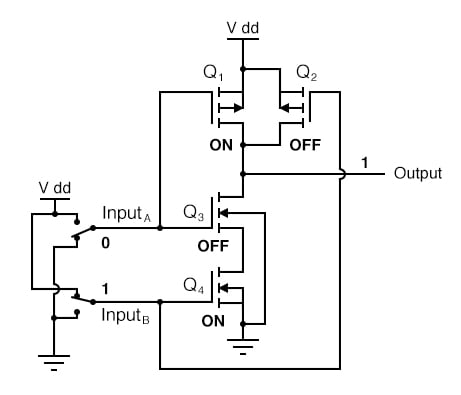

CMOS Kredsløb Adfærd for Alle Indgange Logik

følgende sekvens af illustrationer viser den adfærd af denne NAND-gate for alle fire muligheder i input logisk niveau (00, 01, 10, og 11):

CMOS-OG gate

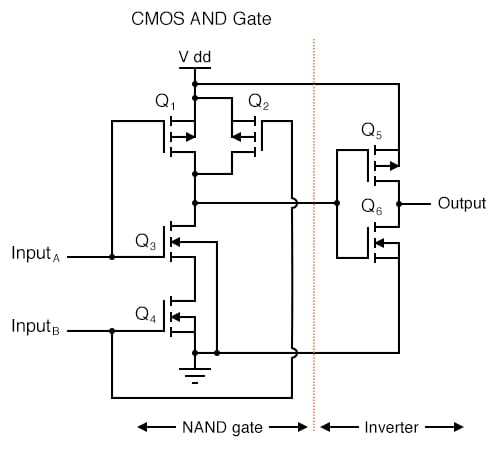

Som med TTL NAND-gate, CMOS-NAND-gate kredsløb kan bruges som udgangspunkt for oprettelsen af en AND-gate., Alle, der skal tilføjes, er en anden fase af transistorer til at invertere output signal:

CMOS ELLER Porte

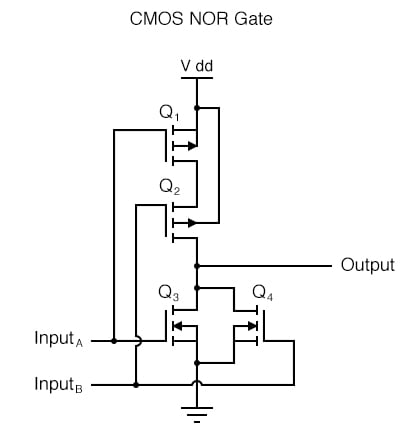

EN CMOS HELLER ikke gate kredsløb bruger fire MOSFETs ligesom NAND-gate, bortset fra at dens transistorer er anderledes arrangeret., I stedet for to parallel sourcing (øvre) transistorer koblet til Vdd og to serie-forbundet synkende (lavere) transistorer forbundet til jorden, og HELLER ikke gate bruger to serie-forbundet sourcing transistorer og to parallel-forbundet synker transistorer som dette:

Som med NAND-gate transistorer Q1 og Q3 arbejde som komplementære par, som gør transistorer Spørgsmål 2 og Spørgsmål 4. Hvert par styres af et enkelt indgangssignal., Hvis enten input A eller input B er ” høje “(1), vil mindst en af de nedre transistorer (33 eller44) være mættet, hvilket gør udgangen” lav ” (0).

kun i tilfælde af, at begge indgange er “lave” (0), vil begge lavere transistorer være i cutoff-tilstand, og begge øvre transistorer være mættede, de betingelser, der er nødvendige for, at output går “højt” (1). Denne adfærd definerer selvfølgelig NOR logic-funktionen.

CMOS eller Porte

OR-funktionen kan opbygges fra basis-eller-porten med tilføjelse af et invertertrin på output:

TTL vs., CMOS: fordele og ulemper

da det ser ud til, at enhver port, der er mulig at konstruere ved hjælp af TTL-teknologi, kan duplikeres i CMOS, hvorfor eksisterer disse to “familier” af logisk design stadig sammen? Svaret er, at både TTL og CMOS har deres egne unikke fordele.

først og fremmest på listen over sammenligninger mellem TTL og CMOS er spørgsmålet om strømforbrug. I dette mål for ydeevne er CMOS den ubestridte victor., Fordi de komplementære P-og N-kanal MOSFET-par i et CMOS-portkredsløb (ideelt) aldrig leder på samme tid, er der ringe eller ingen strøm trukket af kredsløbet fra VDD-strømforsyningen bortset fra hvilken strøm der er nødvendig for at kilde strøm til en belastning. TTL, på den anden side, kan ikke fungere uden nogen strøm trukket på alle tidspunkter, på grund af forspændingskravene fra de bipolære transistorer, hvorfra den er lavet.

Der er dog en advarsel til denne fordel., Mens strømafgivelsen af en TTL-Port forbliver temmelig konstant uanset dens driftstilstand(er), spreder en CMOS-Port mere strøm, når frekvensen af dens indgangssignal(er) stiger. Hvis en CMOS-Port betjenes i en statisk (uændret) tilstand, spreder den nul effekt (ideelt).

CMOS-portkredsløb tegner imidlertid forbigående strøm under hver output-tilstandskontakt fra “lav” til “høj” og vice versa. Så jo oftere en CMOS-Port skifter tilstande, jo oftere trækker den strøm fra Vdd-forsyningen, og dermed større strømafbrydelse ved større frekvenser.,fordele ved CMOS

en CMOS-Port trækker også meget mindre strøm fra en køreportudgang end en TTL-port, fordi MOSFETs er spændingsstyrede, ikke strømstyrede enheder. Dette betyder, at en port kan køre mange flere CMOS-indgange end ttl-indgange. Målet for, hvor mange portindgange en enkelt portudgang kan køre, kaldes fanout.

en anden fordel, at CMOS gate designs nyder over TTL er et meget bredere tilladt udvalg af strømforsyningsspændinger. Mens TTL-porte er begrænset til strømforsyningsspændinger (Vcc) mellem 4, 75 og 5.,25 volt, CMOS-porte er typisk i stand til at fungere på enhver spænding mellem 3 og 15 volt!

årsagen bag denne forskel i strømforsyningsspændinger er de respektive bias krav til MOSFET versus bipolære junction transistorer. MOSFET ‘er styres udelukkende af gate spænding (med hensyn til substrat), mens BJT’ er er strømstyrede enheder.

TTL-portkredsløbsmodstande beregnes nøjagtigt for korrekte forspændingsstrømme under forudsætning af en 5 volt reguleret strømforsyning., Eventuelle væsentlige variationer i denne strømforsyningsspænding vil resultere i, at transistorforspændingsstrømmene er forkerte, hvilket derefter resulterer i upålidelig (uforudsigelig) drift.

den eneste effekt, som variationer i strømforsyningsspænding har på en CMOS-Port, er spændingsdefinitionen for en “høj” (1) tilstand. For en CMOS-port, der arbejder ved 15 volt strømforsyningsspænding (Vdd), skal et indgangssignal være tæt på 15 volt for at blive betragtet som “højt” (1). Spændingstærsklen for et” lavt ” (0) signal forbliver det samme: i nærheden af 0 volt.,

ulemper ved CMOS

en bestemt ulempe ved CMOS er langsom hastighed sammenlignet med TTL. Input capacitances af en CMOS-gate er meget, meget større end for en sammenlignelig TTL gate—på grund af brugen af MOSFETs snarere end Bjt—og så en CMOS-porten vil være langsommere til at reagere på et signal overgang (lav til høj eller omvendt) end en TTL-porten, som alle andre faktorer lige.,

RC – tidskonstanten dannet af kredsløbsmodstande og portens inputkapacitans har en tendens til at hindre de hurtige stignings-og faldtider på et digitalt logisk niveau og derved forringe højfrekvent ydelse.

strategier til bekæmpelse af ulemperne

en strategi til minimering af denne iboende ulempe ved CMOS-portkredsløb er at “buffer” udgangssignalet med yderligere transistortrin for at øge enhedens samlede spændingsforstærkning., Dette giver en hurtigere overgang udgangsspænding (høj til lav eller lav til høj) for en indgangsspænding, der langsomt skifter fra en logisk tilstand til en anden.

Overvej dette eksempel, i en “ikke bufferet” ELLER gate i forhold til en “buffer” eller B-serie, ELLER tor:

I det væsentlige, B-serie design ekstraudstyr tilføjer to invertere til produktionen af en enkelt ELLER kredsløb., Det tjener ikke noget formål, for så vidt som digital logik er bekymret, da to kaskadekoblede invertere blot annuller:

Men, tilføjer disse inverter faser for at kredsløbet ikke tjene det formål at øge den samlede spænding gevinst, at gøre produktionen mere følsomme over for ændringer i input tilstand, der arbejder for at overvinde den iboende træghed, der er forårsaget af CMOS-gate input kapacitans.

anmeldelse:

- CMOS logic gates er lavet af IGFET (MOSFET) transistorer snarere end bipolære junction transistorer.

- CMOS gate indgange er følsomme over for statisk elektricitet., De kan blive beskadiget af høje spændinger, og de kan antage enhver logik niveau, hvis venstre flydende.

- pullup-og pulldo .n-modstande bruges til at forhindre, at en CMOS-portindgang flyder, hvis den drives af en signalkilde, der kun er i stand til at købe eller synke strøm.

- CMOS-porte spreder langt mindre effekt end ækvivalente TTL-porte, men deres strømafledning stiger med Signalfrekvens, hvorimod strømafgivelsen af en TTL-Port er omtrent konstant over en lang række driftsforhold.,CMOS gate-indgange trækker langt mindre strøm end TTL-indgange, fordi MOSFET ‘ er er spændingsstyrede, ikke strømstyrede enheder.

- CMOS-porte er i stand til at operere på et meget bredere vifte af strømforsyning spænding end TTL: typisk 3 til 15 volt versus 4.75 til 5,25 volt til TTL.CMOS-porte har en tendens til at have en meget lavere maksimal driftsfrekvens end TTL-porte på grund af inputkapaciteter forårsaget af MOSFET-porte.CMOS-porte i B-serien har” buffered ” – udgange for at øge spændingsforstærkningen fra input til output, hvilket resulterer i hurtigere udgangsrespons på indgangssignalændringer., Dette hjælper med at overvinde den iboende langsomhed af CMOS-porte på grund af MOSFET-inputkapacitans og RC-tidskonstanten derved genereret.