Bis zu diesem Zeitpunkt war unsere Analyse von Transistor-Logikschaltungen auf das TTL-Konstruktionsparadigma beschränkt, bei dem Bipolartransistoren verwendet werden, und die allgemeine Strategie, schwebende Eingänge gleichzusetzen mit „hohen“ (an Vcc angeschlossenen) Eingängen—und entsprechend der Zulage von „Open-Collector“—Ausgangsstufen-wird beibehalten. Dies ist jedoch nicht die einzige Möglichkeit, Logikgatter zu bauen.,

Feldeffekttransistoren

Feldeffekttransistoren, insbesondere die Insulated-Gate-Variante, können bei der Konstruktion von Gate-Schaltungen verwendet werden. Da IGFETs eher spannungsgesteuert als stromgesteuert sind, ermöglichen sie in der Regel sehr einfache Schaltungsdesigns. Nehmen wir zum Beispiel die folgende Inverterschaltung, die mit P – und N-Kanal-IGFETs gebaut wurde:

Beachten Sie das Etikett“ Vdd “ an der positiven Stromversorgungsklemme., Dieses Etikett folgt der gleichen Konvention wie “ Vcc “ in TTL-Schaltungen: Es steht für die konstante Spannung, die an den Drain eines Feldeffekttransistors in Bezug auf Masse angelegt wird.

Feldeffekttransistoren in Gate-Schaltungen

Niedriger Eingang

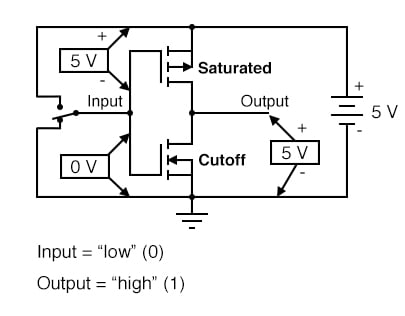

Lassen Sie uns diese Gate-Schaltung an eine Stromquelle und einen Eingangsschalter anschließen und deren Betrieb untersuchen. Bitte beachten sie, dass diese IGFET transistoren sind E-typ (Enhancement-modus), und so sind normalerweise-off geräte.

Es braucht eine angelegte Spannung zwischen Gate und Drain (eigentlich zwischen Gate und Substrat) der richtigen Polarität, um sie einzuschalten.,

Der Obere transistor ist ein P-Kanal-IGFET. Wenn der Kanal (Substrat) positiver als das Gate (Gate negativ in Bezug auf das Substrat) gemacht wird, wird der Kanal verstärkt und Strom zwischen Quelle und Drain erlaubt.

In der obigen Abbildung ist also der obere Transistor eingeschaltet. Der untere Transistor mit Nullspannung zwischen Gate und Substrat (Quelle) befindet sich in seinem normalen Modus: aus.,

Somit ist die Wirkung dieser beiden Transistoren derart, dass die Ausgangsklemme der Gate-Schaltung eine feste Verbindung zu Vdd und eine sehr hohe Widerstandsverbindung zu Masse aufweist. Dies macht den Ausgang “ hoch „(1) für den Zustand“ niedrig “ (0) des Eingangs.,

Hoher Eingang

Als nächstes bewegen wir den Eingangsschalter in seine andere Position und sehen, was passiert:

Jetzt ist der untere Transistor (N-Kanal) gesättigt, da er über eine ausreichende Spannung mit der richtigen Polarität zwischen Gate und Substrat (Kanal) verfügt, um ihn einzuschalten (positiv am Gate, negativ am Kanal). Der obere Transistor mit Nullspannung zwischen Gate und Substrat befindet sich in seinem normalen Modus: aus.

Somit ist der Ausgang dieser Gate-Schaltung nun “ low “ (0)., Diese Schaltung zeigt eindeutig das Verhalten eines Wechselrichters oder NICHT Gatters.

Komplementäre Metalloxidhalbleiter (CMOS)

Die Verwendung von Feldeffekttransistoren anstelle von Bipolartransistoren hat das Design des Invertergatters erheblich vereinfacht. Beachten Sie, dass der Ausgang dieses Gatters niemals schwebt, wie dies bei der einfachsten TTL-Schaltung der Fall ist: Es verfügt über eine natürliche „totempolige“ Konfiguration, die sowohl Laststrom beziehen als auch senken kann.

Der Schlüssel zum eleganten Design dieser Gate-Schaltung ist die ergänzende Verwendung von P-und N-Kanal-IGFETs., Da IGFETs häufiger als MOSFETs (Metal-Oxide-Semiconductor Field Effect Transistor) bekannt sind und diese Schaltung sowohl P – als auch N-Kanal-Transistoren zusammen verwendet, ist die allgemeine Klassifizierung für Gate-Schaltungen wie diese CMOS: Komplementärer Metalloxid-Halbleiter.

CMOS-Gates: Herausforderungen und Lösungen

CMOS-Schaltungen werden nicht von den inhärenten Nichtlinearitäten der Feldeffekttransistoren geplagt, da ihre Transistoren als digitale Schaltungen immer im gesättigten oder abgeschnittenen Modus und niemals im aktiven Modus arbeiten., Ihre Eingänge sind jedoch empfindlich gegenüber hohen Spannungen, die durch elektrostatische (statische Elektrizität) Quellen erzeugt werden, und können sogar durch falsche Spannungsquellen in „hohe“ (1) oder „niedrige“ (0) Zustände aktiviert werden, wenn sie schweben gelassen werden.

Aus diesem Grund ist es nicht ratsam, einen CMOS-Logikgattereingang unter allen Umständen schweben zu lassen. Bitte beachten Sie, dass dies sich stark vom Verhalten eines TTL-Gatters unterscheidet, bei dem ein schwebender Eingang sicher als „hoher“ (1) Logikpegel interpretiert wurde.,

CMOS-Probleme mit schwebenden Eingängen

Dies kann ein Problem verursachen, wenn der Eingang zu einem CMOS-Logikgatter von einem Single-Throw-Schalter angetrieben wird, wobei der Eingang in einem Zustand fest mit Vdd oder Masse verbunden ist und der andere Zustand den Eingang schwebend hat (mit nichts verbunden):

Dieses Problem tritt auch auf, wenn ein CMOS-Gate-Eingang von einem Open-Collector-TTL-Gate angetrieben wird., Da der Ausgang eines solchen TTL-Gatters schwebt, wenn er „hoch“ geht (1), bleibt der CMOS-Gate-Eingang in einem unsicheren Zustand:

Lösung für schwebende Eingänge

Pullup-Widerstände

Glücklicherweise gibt es eine einfache Lösung für dieses Dilemma, eine, die häufig in CMOS-Logikschaltkreisen verwendet wird., Wann immer ein Single-Throw-Schalter (oder eine andere Art von Gate-Ausgang, der sowohl Sourcing-als auch Sinkstrom nicht aufnehmen kann) verwendet wird, um einen CMOS-Eingang anzutreiben, kann ein Widerstand verwendet werden, der entweder an Vdd oder Masse angeschlossen ist, um einen stabilen Logikpegel für den Zustand bereitzustellen, in dem der Ausgang des Antriebsgeräts schwebt.

Der Wert dieses Widerstands ist nicht kritisch: Normalerweise reichen 10 kΩ aus., Bei Verwendung zur Bereitstellung eines“ hohen“(1) Logikpegels im Falle einer schwebenden Signalquelle wird dieser Widerstand als Pullup-Widerstand bezeichnet:

Pulldown-Widerstände

Wenn ein solcher Widerstand verwendet wird, um einen“ niedrigen “ (0) Logikpegel im Falle einer schwebenden Signalquelle bereitzustellen, wird er als Pullup-Widerstand bezeichnet., Auch hier ist der Wert für einen Pulldown-Widerstand nicht kritisch:

Da Open-Collector-TTL-Ausgänge immer sinken, niemals Quelle, Strom, Pullup-Widerstände erforderlich sind, wenn ein solcher Ausgang an einen CMOS-Gate-Eingang angeschlossen wird:

Mehrere Pullup-und Pulldown-Widerstände

Obwohl die CMOS-Gates, die in den vorhergehenden Beispielen verwendet wurden, waren alle Wechselrichter (Single-Input), das gleiche Prinzip von Pullup-und Pulldown-Widerständen gilt für CMOS-Gates mit mehreren Eingängen., Natürlich wird für jeden Gate-Eingang ein separater Pullup-oder Pulldown-Widerstand benötigt:

Dies bringt uns zur nächsten Frage: Wie entwerfen wir CMOS-Gatter mit mehreren Eingängen wie AND, NAND, OR und NOR? Es überrascht nicht, dass die Antwort(en) auf diese Frage eine Einfachheit des Designs zeigt, ähnlich der des CMOS-Wechselrichters gegenüber seinem TTL-Äquivalent.,

CMOS-NAND-Gatter

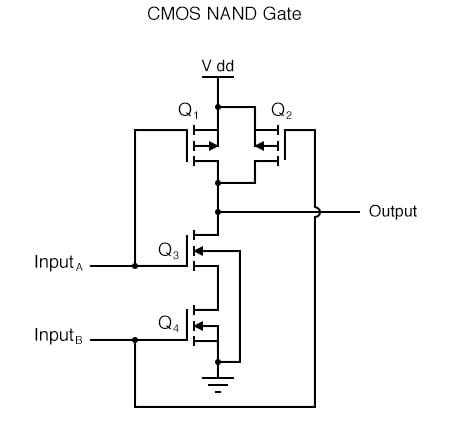

Hier ist zum Beispiel das schematische Diagramm für ein CMOS-NAND-Gatter:

Beachten Sie, wie Transistoren Q1 und Q3 dem in Serie geschalteten Komplementärpaar aus der Wechselrichterschaltung ähneln. Beide werden durch das gleiche Eingangssignal (Eingang A) gesteuert, wobei sich der obere Transistor ausschaltet und der untere Transistor einschaltet, wenn der Eingang „hoch“ (1) ist, und umgekehrt.,

Beachten Sie auch, wie Transistoren Q2 und Q4 ähnlich durch das gleiche Eingangssignal gesteuert werden (Eingang B), und wie sie auch das gleiche Ein/Aus-Verhalten für die gleichen Eingangslogikpegel aufweisen. Die oberen Transistoren beider Paare (Q1 und Q2) haben ihre Quell-und Abflussklemmen parallel, während die unteren Transistoren (Q3 und Q4) in Reihe geschaltet sind.

Dies bedeutet, dass der Ausgang „hoch“ (1) geht, wenn einer der oberen Transistoren gesättigt ist, und nur dann „niedrig“ (0) geht, wenn beide unteren Transistoren gesättigt sind.,

CMOS-Schaltungsverhalten für alle Logikeingänge

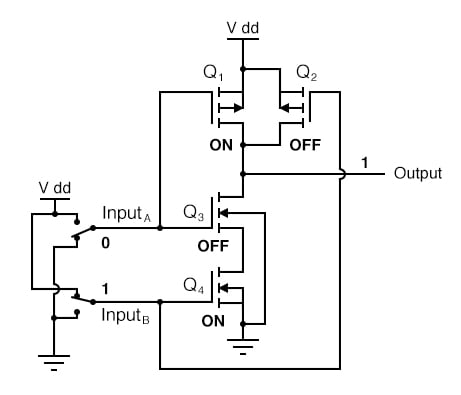

Die folgende Abfolge von Abbildungen zeigt das Verhalten dieses NAND-Gatters für alle vier Möglichkeiten der Eingangslogikpegel (00, 01, 10 und 11):

CMOS UND Gate

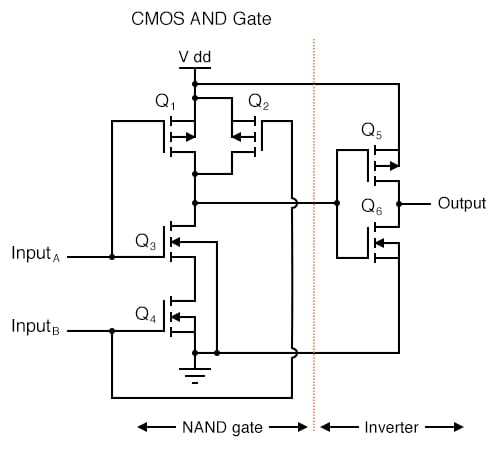

Wie beim TTL-NAND-Gate kann die CMOS-NAND-Gate-Schaltung als Ausgangspunkt für die Erstellung von AN UND Gate verwendet werden., Alles, was hinzugefügt werden muss, ist eine weitere Stufe von Transistoren, um das Ausgangssignal umzukehren:

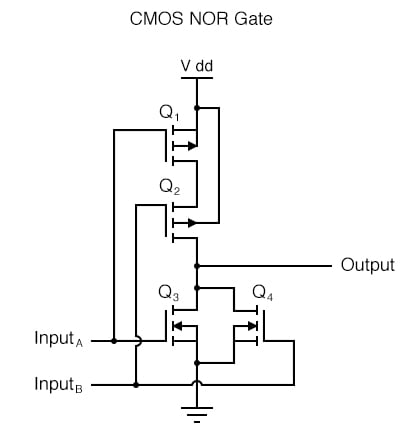

CMOS – NOR-Gates

Eine CMOS – NOR-Gate-Schaltung verwendet vier MOSFETs genau wie das NAND-Gate, mit der Ausnahme, dass ihre Transistoren unterschiedlich angeordnet sind., Anstelle von zwei parallelen Sourcing (oberen) Transistoren, die mit Vdd verbunden sind, und zwei seriell verbundenen sinkenden (unteren) Transistoren, die mit Masse verbunden sind, verwendet das NOR-Gate zwei seriell verbundene Sourcing-Transistoren und zwei parallel verbundene sinkende Transistoren wie folgt:

Wie beim NAND-Gate arbeiten die Transistoren Q1 und Q3 als komplementäres Paar, ebenso wie die Transistoren Q2 und Q4. Jedes Paar wird durch ein einzelnes Eingangssignal gesteuert., Wenn entweder Eingang A oder Eingang B „hoch“ (1) sind, wird mindestens einer der unteren Transistoren (Q3 oder Q4) gesättigt, wodurch der Ausgang „niedrig“ (0) wird.

Nur für den Fall, dass beide Eingänge „niedrig“ (0) sind, befinden sich beide unteren Transistoren im Cutoff-Modus und beide oberen Transistoren sind gesättigt, die Bedingungen, die erforderlich sind, damit der Ausgang „hoch“ wird (1). Dieses Verhalten definiert natürlich die NOR-Logikfunktion.

CMOS ODER Gates

Die OR-Funktion kann aus dem Basic NOR Gate mit Zusatz einer Inverterstufe am Ausgang aufgebaut werden:

TTL vs., CMOS: Vor-und Nachteile

Da anscheinend jedes Gate, das mit der TTL-Technologie konstruiert werden kann, in CMOS dupliziert werden kann, warum existieren diese beiden „Familien“ des Logikdesigns immer noch? Die Antwort ist, dass sowohl TTL als auch CMOS ihre eigenen einzigartigen Vorteile haben.

In erster Linie auf der Liste der Vergleiche zwischen TTL und CMOS ist die Frage des Stromverbrauchs. In diesem Maß an Leistung ist CMOS der unangefochtene Sieger., Da die komplementären P – und N-Kanal-MOSFET-Paare einer CMOS-Gate-Schaltung (idealerweise) niemals gleichzeitig leitend sind, wird von der Schaltung nur wenig oder gar kein Strom von der Vdd-Stromversorgung gezogen, mit Ausnahme dessen, welcher Strom zur Stromquelle erforderlich ist eine Last. TTL hingegen kann aufgrund der Vorspannungsanforderungen der Bipolartransistoren, aus denen es hergestellt wird, nicht jederzeit ohne Strom funktionieren.

Es gibt jedoch einen Vorbehalt zu diesem Vorteil., Während die Verlustleistung eines TTL-Gatters unabhängig von seinem Betriebszustand(seinen Betriebszuständen) ziemlich konstant bleibt, leitet ein CMOS-Gate mehr Leistung ab, wenn die Frequenz seines Eingangssignals(seiner Eingangssignale) ansteigt. Wenn ein CMOS-Gate in einem statischen (unveränderlichen) Zustand betrieben wird, leitet es (idealerweise) keine Leistung ab.

CMOS-Gate-Schaltungen ziehen jedoch bei jedem Ausgangszustandsschalter von „low“ auf „high“ transienten Strom und umgekehrt. Je öfter ein CMOS-Gate die Modi wechselt, desto häufiger zieht es Strom aus der Vdd-Versorgung, daher eine größere Verlustleistung bei größeren Frequenzen.,

Vorteile von CMOS

Ein CMOS-Gate zieht auch viel weniger Strom von einem treibenden Gate-Ausgang als ein TTL-Gate, da MOSFETs spannungsgesteuerte, nicht stromgesteuerte Geräte sind. Dies bedeutet, dass ein Gate viel mehr CMOS-Eingänge als TTL-Eingänge ansteuern kann. Das Maß dafür, wie viele Gate-Eingänge ein einzelner Gate-Ausgang ansteuern kann, wird als Fanout bezeichnet.

Ein weiterer Vorteil, den CMOS-Gate-Designs gegenüber TTL genießen, ist ein viel breiterer zulässiger Bereich von Versorgungsspannungen. Während TTL-Gates auf Versorgungsspannungen (Vcc) zwischen 4,75 und 5 beschränkt sind.,25 Volt, CMOS-Gates sind normalerweise in der Lage, mit jeder Spannung zwischen 3 und 15 Volt zu arbeiten!

Der Grund für diese Ungleichheit bei den Versorgungsspannungen sind die jeweiligen Bias-Anforderungen von MOSFET gegenüber bipolaren Übergangstransistoren. MOSFETs werden ausschließlich durch Gate-Spannung (in Bezug auf Substrat) gesteuert, während BJTs stromgesteuerte Geräte sind.

TTL gate schaltung widerstände sind genau berechnet für richtige bias ströme unter der annahme eine 5 volt geregelte netzteil., Alle signifikanten Schwankungen dieser Versorgungsspannung führen dazu, dass die Transistorvorspannungsströme falsch sind, was dann zu einem unzuverlässigen (unvorhersehbaren) Betrieb führt.

Der einzige Effekt, den Variationen der Versorgungsspannung auf ein CMOS-Gate haben, ist die Spannungsdefinition eines“ hohen “ (1) Zustands. Für ein CMOS-Gate, das mit 15 Volt Versorgungsspannung (Vdd) arbeitet, muss ein Eingangssignal nahe 15 Volt liegen, um als „hoch“ angesehen zu werden (1). Die Spannungsschwelle für ein“ niedriges “ (0) Signal bleibt gleich: nahe 0 Volt.,

Nachteile von CMOS

Ein wesentlicher Nachteil von CMOS ist die langsame Geschwindigkeit im Vergleich zu TTL. Die Eingangskapazitäten eines CMOS-Gatters sind viel, viel größer als die eines vergleichbaren TTL-Gatters-aufgrund der Verwendung von MOSFETs anstelle von BJTs – und so reagiert ein CMOS-Gate langsamer auf einen Signalübergang (niedrig-zu-hoch oder umgekehrt) als ein TTL-Gate, wobei alle anderen Faktoren gleich sind.,

Die durch Schaltungswiderstände gebildete RC-Zeitkonstante und die Eingangskapazität des Gatters neigen dazu, die schnellen Anstiegs – und Abfallzeiten eines digitalen Logikpegels zu behindern, wodurch die Hochfrequenzleistung beeinträchtigt wird.

Strategien zur Bekämpfung der Nachteile

Eine Strategie zur Minimierung dieses inhärenten Nachteils der CMOS-Gate-Schaltung besteht darin, das Ausgangssignal mit zusätzlichen Transistorstufen zu „puffern“, um die Gesamtspannungsverstärkung des Geräts zu erhöhen., Dies liefert eine schneller übergreifende Ausgangsspannung (High-to-Low oder Low-to-High) für eine Eingangsspannung, die sich langsam von einem logischen Zustand in einen anderen ändert.

Betrachten Sie dieses Beispiel eines“ ungepufferten „NOR-Gatters im Vergleich zu einer „gepufferten“oder B-Serie oder einem Gate:

Im Wesentlichen fügt die Entwurfsverbesserung der B-Serie dem Ausgang einer einfachen NOR-Schaltung zwei Wechselrichter hinzu., Dies dient in Bezug auf die digitale Logik keinem Zweck, da zwei kaskadierte Wechselrichter einfach abbrechen:

Das Hinzufügen dieser Wechselrichterstufen zur Schaltung dient jedoch dem Zweck, die Gesamtspannungsverstärkung zu erhöhen, wodurch der Ausgang empfindlicher auf Änderungen des Eingangszustands reagiert und die durch die CMOS-Gate-Eingangskapazität verursachte inhärente Langsamkeit überwunden wird.

REVIEW:

- CMOS Logik-Gatter sind aus IGFET (MOSFET) – transistoren eher als bipolar junction transistoren.

- CMOS-gate-Eingänge sind empfindlich auf statische Elektrizität., Sie können durch hohe Spannungen beschädigt werden, und sie können jeden Logikpegel annehmen, wenn sie schweben gelassen werden.

- Pullup-und Pulldown-Widerstände werden verwendet, um zu verhindern, dass ein CMOS-Gate-Eingang schwebt, wenn er von einer Signalquelle angetrieben wird, die nur Strom beziehen oder absenken kann.

- CMOS-Gates leiten weit weniger Strom ab als äquivalente TTL-Gates, aber ihre Verlustleistung steigt mit der Signalfrequenz, während die Verlustleistung eines TTL-Gates über einen weiten Bereich von Betriebsbedingungen ungefähr konstant ist.,

- CMOS-Gate-Eingänge ziehen weit weniger Strom als TTL-Eingänge, da MOSFETs spannungsgesteuerte, nicht stromgesteuerte Geräte sind.

- CMOS-Gates können mit einem viel größeren Bereich von Versorgungsspannungen als TTL betrieben werden: typischerweise 3 bis 15 Volt gegenüber 4,75 bis 5,25 Volt für TTL.

- CMOS-Gates haben aufgrund der durch die MOSFET-Gates verursachten Eingangskapazitäten tendenziell eine viel niedrigere maximale Betriebsfrequenz als TTL-Gates.

- CMOS-Gates der B-Serie verfügen über“ gepufferte “ Ausgänge, um die Spannungsverstärkung von Eingang zu Ausgang zu erhöhen, was zu einer schnelleren Ausgangsreaktion auf Eingangssignaländerungen führt., Dies hilft, die inhärente Langsamkeit von CMOS-Gates aufgrund der MOSFET-Eingangskapazität und der dadurch erzeugten RC-Zeitkonstante zu überwinden.